# Lattice VHDL Training Part I

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 1

## VHDL

# **Basic Modeling Structure**

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 2

## **VHDL Design Description**

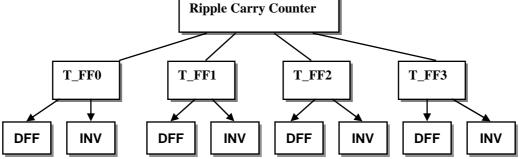

• VHDL language describes a digital system as a set of modular blocks. Each modular block is described by a pair of **entity** and **architecture**.

| entity counter | architecture counter_design of counter |  |  |

|----------------|----------------------------------------|--|--|

| ••••           | ••••                                   |  |  |

| end counter;   | end counter_design;                    |  |  |

| entity tff     | architecture tff_design of tff is      |  |  |

| ••••           | ••••                                   |  |  |

| end tff;       | end tff;                               |  |  |

| entity inv     | architecture inv_design of inv         |  |  |

| ••••           | ••••                                   |  |  |

| end inv;       | end inv_design;                        |  |  |

| entity dff     | architecture dff_design of dff is      |  |  |

| ••••           | ••••                                   |  |  |

| end dff:       | end dff:                               |  |  |

|                | Ripple Carry Counter                   |  |  |

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 3

## **VHDL Design Descriptions**

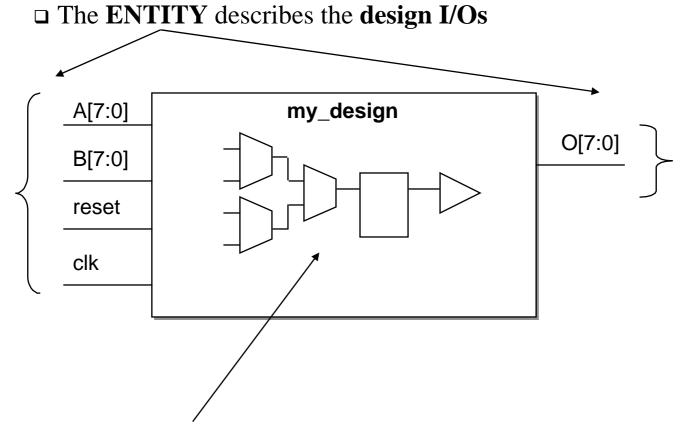

• VHDL design description consist of an ENTITY and ARCHITECTURE pair

□ The **ARCHITECTURE** describes the **content of the design**

© LATTICE SEMICONDUCTOR CORPORATION 1998

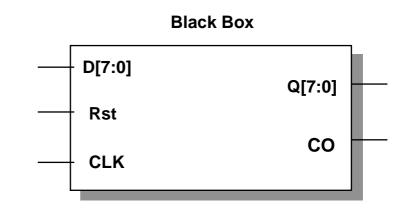

• VHDL description of the entity:

**ENTITY** black\_box **is**

| port ( | rst : | <b>IN</b> std_logic; |

|--------|-------|----------------------|

|        |       |                      |

- clk : **IN** std\_logic;

- d : IN std\_logic\_vector (7 downto 0);

- q : BUFFER std\_logic\_vector (7 downto 0);

- co : OUT std\_logic );

END black\_box;

Lattice

VANTIS

#### • Note: VHDL is **NOT** case sensitive!

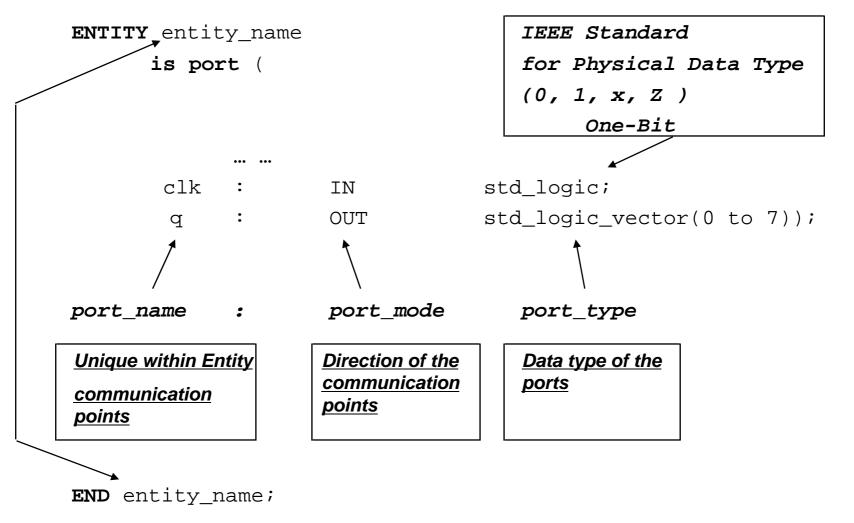

## **The Entity - General Format for Port Declaration**

• Entity **<u>only</u>** describes the circuit **<u>interface</u>** but not function

© LATTICE SEMICONDUCTOR CORPORATION 1998

LATTICE PROPRIETARY

Lattice

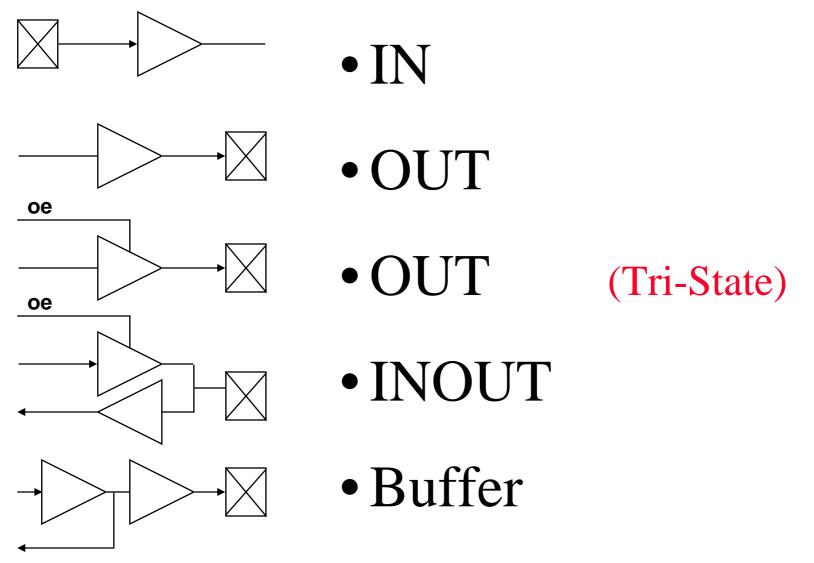

### **PORT Modes**

© LATTICE SEMICONDUCTOR CORPORATION 1998

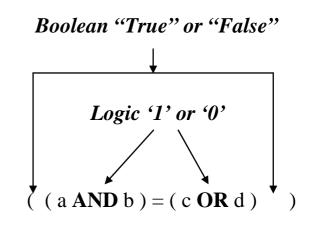

- **integer** Useful as index holders for loops and constants. When used for I/O signals, usually reference counters

- **Boolean** Can take values of 'TRUE' and 'FALSE'

- std\_logic

- std\_logic\_vector

- '1', 'X', and Z' defined by IEEE std 1164.A grouping of std\_logic, standard industry logic type

Standard industry logic type, has values of '0',

## **PORT Types**

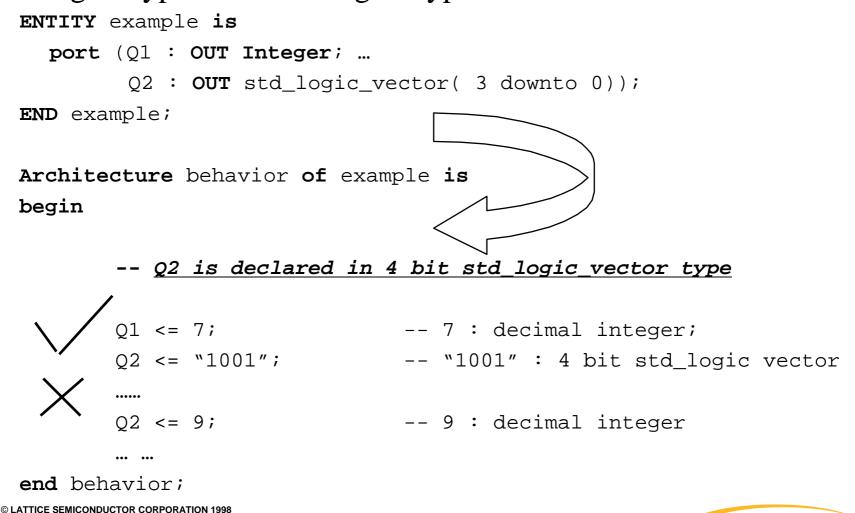

• VHDL is a strongly typed language. You cannot assign one signal type to another signal type.

Lattice

VANTIS

FAE Training VHDL Training

February 2000 9

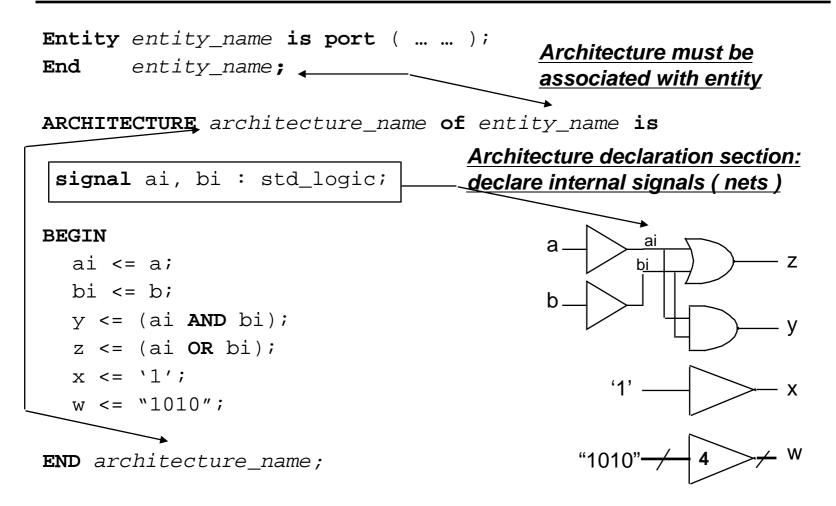

## **The Architecture body - General Format**

© LATTICE SEMICONDUCTOR CORPORATION 1998

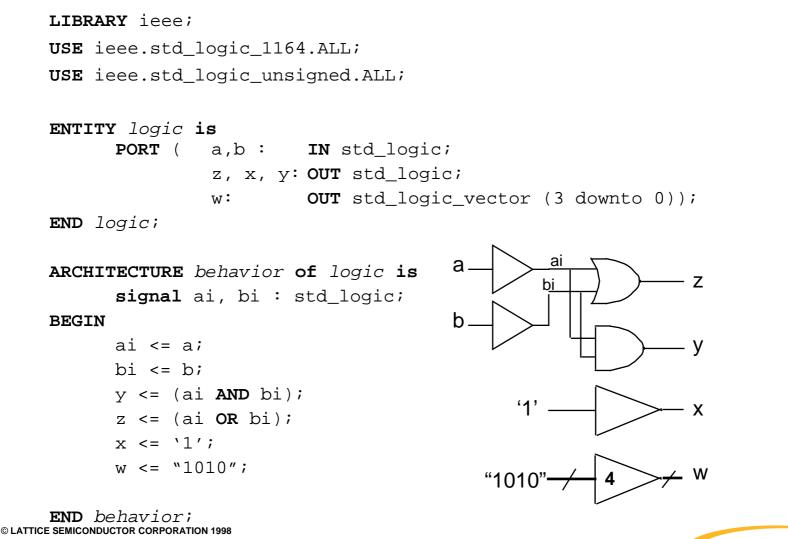

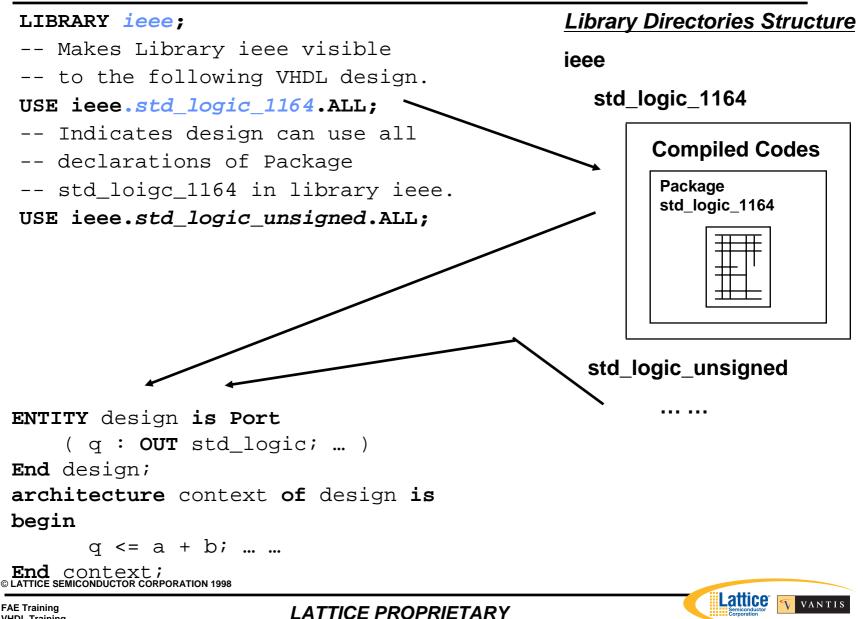

## **Entity / Architecture / Libraries - example**

• Every design has an ENTITY/ARCHITECTURE pair

LATTICE PROPRIETARY

FAE Training VHDL Training February 2000 11 Lattice Semiconductor Corporation

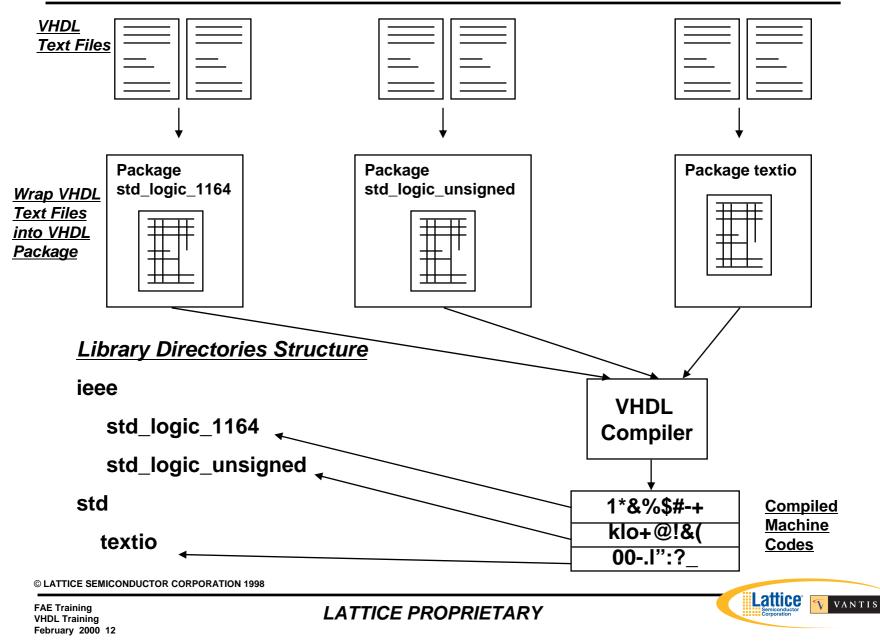

## Libraries

## Libraries

• Library is a place to keep *precompiled packages* so that they can be used in other VHDL designs

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

```

```

ieee - symbolic name for IEEE standard library.

Contains packages std_logic_1164,

std_logic_unsigned, etc.

```

```

std_logic_1164 - name of the VHDL package

Package std_logic_1164 contains declaration

of data type for std_logic and

std_logic_vector.

```

```

std_logic_unsigned - name of the VHDL package.

Package std_logic_unsigned contains the

declaration of operators, functions for

std_logic and std_logic_vector arithmetic

operations.

```

## Libraries

VHDL Training February 2000 14

# VHDL Language Syntax & VHDL Design Methods

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 15

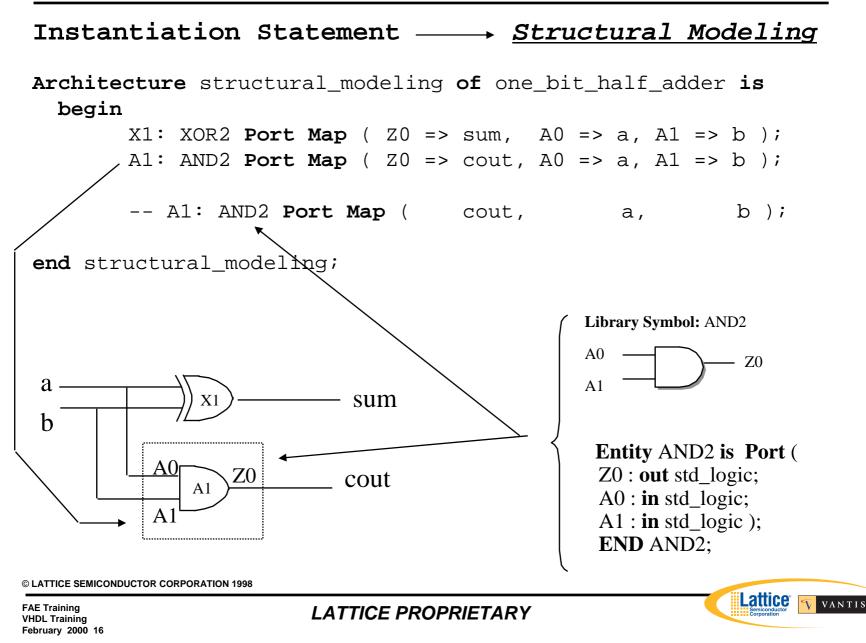

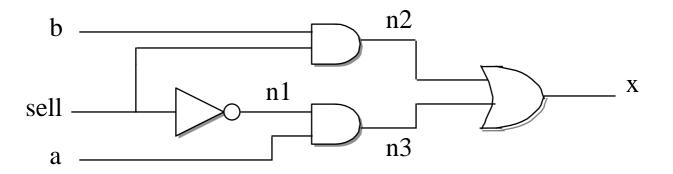

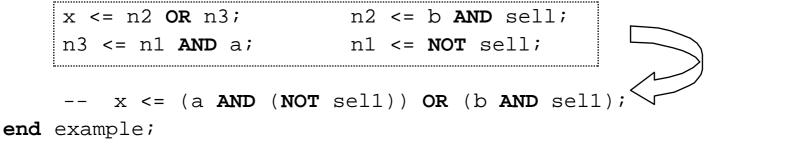

### **Concurrent Statement**

## **Concurrent Statement**

## • Dataflow Modeling by

□ boolean equations assignments

□ conditional assignments (When-Else, With-Select-When)

Architecture dataflow\_modeling of example is

signal n1, n2, n3 : std\_logic; -- Declare Internal Nets

begin

Lattice

VANTI

© LATTICE SEMICONDUCTOR CORPORATION 1998

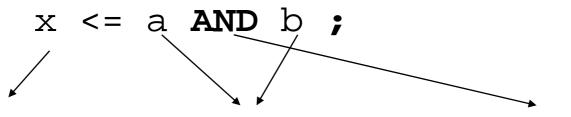

**Concurrent Statement - Boolean Equation Assignment**

Boolean Equation Assignment Format

Left Operand Right Operands Operator

The '<=' operation is also used to signify 'taking on the value of'

Concatenate Assignment

$c \le a(2 \text{ downto } 0) \& b(3 \text{ downto } 0);$

$$c(6) \le a(2); c(5) \le a(1); c(4) \le a(0);$$

$c(3) \le b(3); c(2) \le b(2); c(1) \le b(1); c(0) \le b(0);$

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

## **Standard VHDL Operators**

Logical Operators

AND

OR

XOR

NOT

a, b, c, d : std\_logic

Relational Operators

- = Equal to

- /= Not equal to

- > Greater than

- < Less than

- >= Greater than or equal to

- <= Less than or equal to

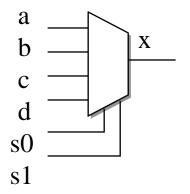

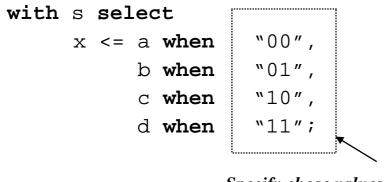

## **Concurrent Conditional Assignment**

- With-Select-When

- Example

```

entity mux is port (

a, b, c, d:in std_logic;

s: in std_logic_vector(1 downto 0);

x: out std_logic );

end mux;

architecture archmux of mux is

begin

with s select

x <= a when "00", -- x is assigned based on s

b when "01",

c when "10",</pre>

```

```

d when "11";

```

end archmux;

© LATTICE SEMICONDUCTOR CORPORATION 1998

LATTICE PROPRIETARY

Χ

a

b

C

d

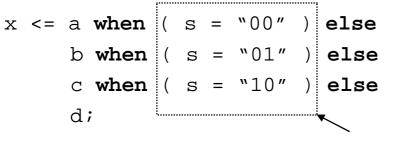

## **Concurrent conditional Assignment**

- When-Else

- Same example of 4-to-1 mux

architecture archmux of mux is

begin

x <= a when ( s = "00" ) else

b when ( s = "01" ) else

c when ( s = "10" ) else

d;

end archmux;</pre>

Lattice

VANTIS

• WITH-SELECT-WHEN must specify all mutually exclusive conditions

• WHEN-ELSE does not have to

## With-Select-When vs. WHEN-ELSE

Specify chose values based

on data type of "S"

**Specify Boolean conditions**

• Specify all mutual exclusive conditions

• Don't have to specify all mutually exclusive conditions, the last one can be defaulted after "ELSE" keyword

© LATTICE SEMICONDUCTOR CORPORATION 1998

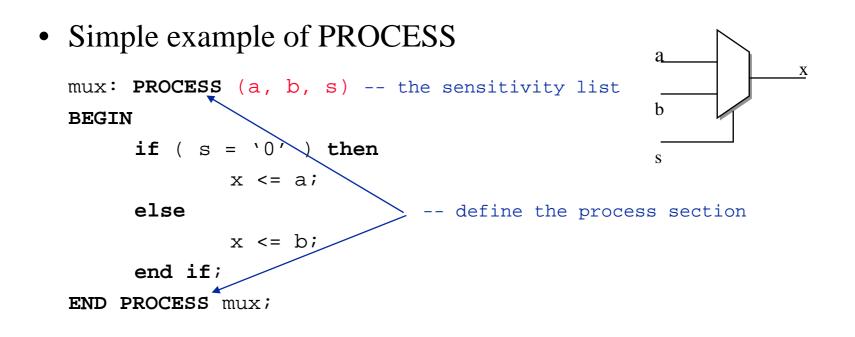

## **Sequential Statements**

- Process Statement \_\_\_\_\_ *Behavioral Modeling*

- A PROCESS is used to describe <u>sequential</u> events and is included in the ARCHITECTURE of the design.

- An ARCHITECTURE can contain several PROCESS statements.

- PROCESS statements have 3 parts:

□ Sensitivity list :

- includes signals used in the PROCESS

- process is active when a signal in sensitivity list changes value

**PROCESS** :

- the description of behavior

- **BEGIN END PROCESS** statement:

- describes the beginning & ending of the PROCESS

• Here the process 'mux' is sensitive to signals 'a', 'b' and 's'. Whenever signal 'a' or 'b' or 's' changes value, the statements inside the process will be evaluated

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

## **IF - THEN - ELSE**

- It is a <u>sequential</u> statement and can only be used in PROCESS

- To select a specific execution path based on Boolean evaluation of a condition or set of conditions

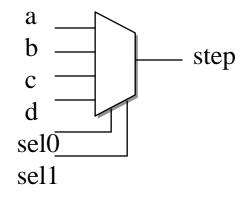

- Cascaded If-Then-Else

```

PROCESS (select, a, b, c, d)

BEGIN

if (select = "00") then

step <= a;

elsif (select = "01") then

step <= b;

elsif (select = "10") then

step <= c;

else

step <= d;

end if;

END PROCESS;</pre>

```

- ELSIF allows multiple conditions in one statement

- Must have an "END IF" statement for every "IF" statement

• Nested If-Then-Else

```

PROCESS (select, a, b, c, d)

BEGIN

if (select = "00") then

step <= a;</pre>

else

a

if (select = "01") then

b

step <= b;</pre>

step

else

С

if (select = "10") then

d

step <= c;</pre>

sel0

else

step <= d;

sel1

end if;

end if;

end if;

```

```

END PROCESS;

```

Semiconductor Corporation

It is a sequential statement and can only be used in PROCESS

ARCHITECTURE archdesign OF design IS

BEGIN

decode: PROCESS (a, b, c, option)

BEGIN

CASE option IS

WHEN "00" => output <= a;

WHEN "01" => output <= b;

WHEN "10" => output <= c;

WHEN OTHERS => output <= '0';

END CASE;

END PROCESS decode;</pre>

- **END** archdesign;

- **OTHERS** is all other possible value for signals of type std\_logic

#### • SIGNAL

**Data Objects**

□ used to declare <u>internal</u> signals; not external signals

□ interconnects components

□ may be assigned to an external signal

```

ARCHITECTURE behavior of example is

SIGNAL count: std_logic_vector (3 downto 0);

SIGNAL flag: integer;

SIGNAL mtag: integer range 0 to 15;

SIGNAL stag: integer range 100 downto 0;

BEGIN

```

```

--mtag is a 4-bit array; MSB is mtag(0); LSB is mtag(3)

--stag is a 7-bit array; MSB is stag(6); LSB is stag(0)

--always declared in ARCHITECTURE section

```

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

## **Data Objects**

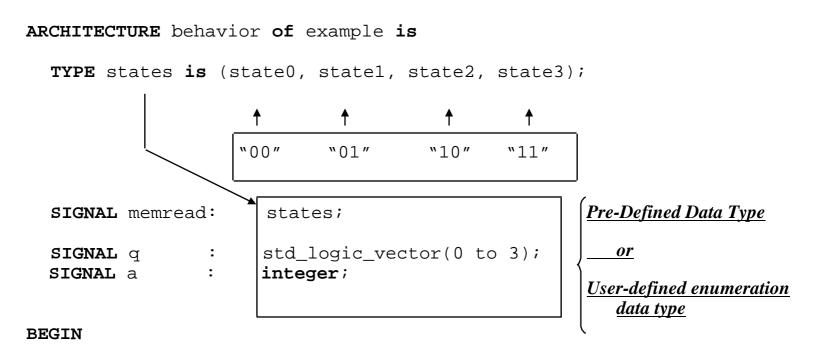

• SIGNAL in User-defined enumeration type

□ represents state elements in a state-machine

--each state (state0, state1, etc) represents a distinct state.

© LATTICE SEMICONDUCTOR CORPORATION 1998

### • CONSTANT

holds a specific value of a type that cannot be changed within the design description

```

ARCHITECTURE behavior of example is

CONSTANT width: integer := 8;

```

```

BEGIN

```

-- "width" is a constant with integer type and has a value of "8"

• VARIABLE

□ used to declare <u>local values</u> only within a given PROCESS.

```

PROCESS (s)

VARIABLE result: integer := 12;

BEGIN

-- "result" is a VARIABLE with an intial value of "12".

-- value of "result" may be modified within a PROCESS.

• variable assignment use :=

• port/signal assignment use <=</pre>

```

© LATTICE SEMICONDUCTOR CORPORATION 1998

LATTICE PROPRIETARY

Lattice

# Understand VHDL Synthesis and

## **VHDL Design Application**

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 31 LATTICE PROPRIETARY

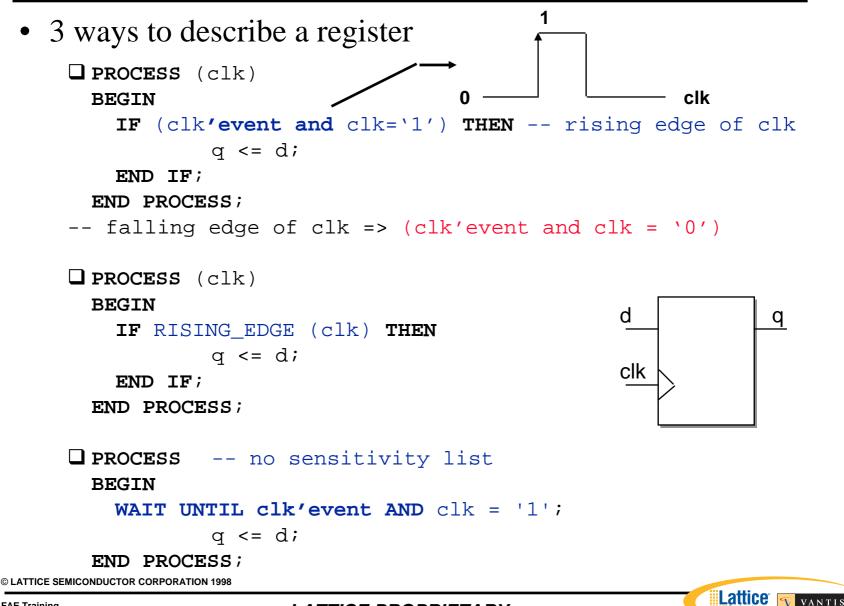

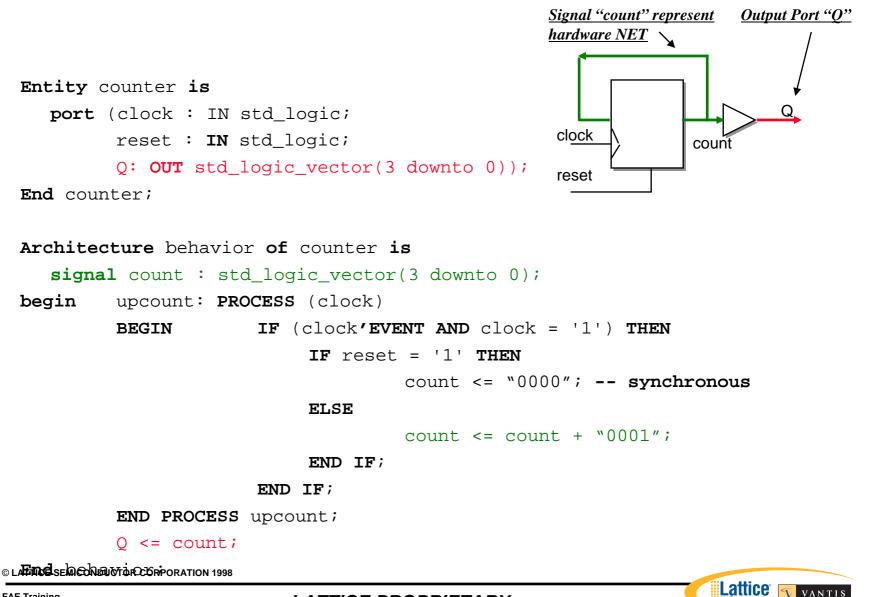

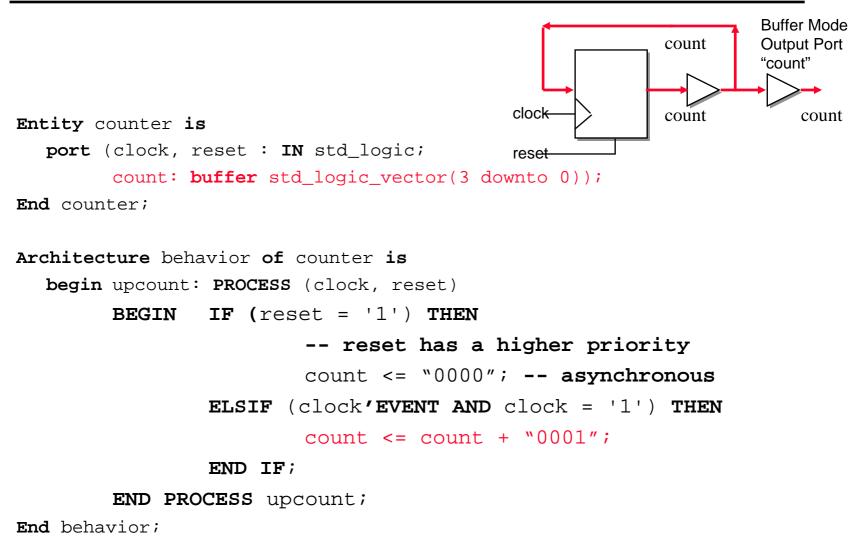

## **REGISTERS in Behavioral VHDL**

## Synchronous/Asynchronous Reset Register

**ARCHITECTURE** behavior **of** synchronous\_reset\_register **is BEGIN**

ARCHITECTURE behavior of Asynchronous\_reset\_register is BEGIN

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

## **LATCHES - in Behavioral VHDL**

**ARCHITECTURE** behavior of d latch is BEGIN **PROCESS** (enable) outa ina BEGIN **IF** (enable = '1') **then** enable outa <= ina; END IF; END PROCESS; **END** behavior; ARCHITECTURE behavior of set\_reset\_latch is BEGIN **PROCESS** (set, reset) outa set BEGIN IF (set = '1' AND reset = '0') then reset outa <= '1'; ELSIF (set = '0' AND reset = '1') then outa  $\leq '0';$ END IF; END PROCESS; **END** behavior;

## Synchronous/Asynchronous Reset Latch

**ARCHITECTURE** behavior **of** synchronous\_reset\_d\_latch **is BEGIN**

**ARCHITECTURE** behavior **of** asynchronous\_reset\_d\_latch **is BEGIN**

## **Output Enables**

Entity design is port ( q : out std\_logic\_vector(0 to 6); ...); End design; -- Tri-State Port declared as OUT

ARCHITECTURE behavioral of design is

BEGIN

```

q <= qint when (oe='1') else "ZZZZZZZ" ;</pre>

```

**END** behavioral;

ARCHITECTURE behavioral of design is

© LATTICE SEMICONDUCTOR CORPORATION 1998

LATTICE PROPRIETARY

q

Lattice

## **Bi-Directional Port**

```

Entity design is port(-- Bi-Directional Port declared as INOUT

data:inout std logic vector(0 to 7);...);

End design;

ARCHITECTURE behavior OF design IS

SIGNAL ext input : std logic;

BEGIN

data \leq count WHEN oe = '1' ELSE "ZZZZZZZZZ';

ext input <= data;

END behavior;

ARCHITECTURE behavior OF design IS

oe

SIGNAL ext input : std logic;

data

BEGIN

PROCESS (oe)

count

BEGIN

IF (oe = 1') THEN

ext input

data <= count;

ELSE

data <= "ZZZZZZZZ";</pre>

END IF;

END PROCESS;

ext input <= data;</pre>

END behavior;

```

© LATTICE SEMICONDUCTOR CORPORATION 1998

Lattice

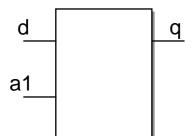

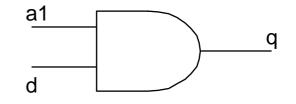

## **CPLD Optimization - Caution using "If-Then-Else"**

The following VHDL file does

The following VHDL file not specify the value of "q" when "a1" is equal to "0", thus creating a "Latch".

```

PROCESS (a1, d)

```

BEGIN

IF (a1 = `1') then

a <= di

END PROCESS;

© LATTICE SEMICONDUCTOR CORPORATION 1998

specifies the value of "q" when "a1" is equal to "0", thus creating an AND gate

1

## **CPLD Optimization - Caution using "Case-When"**

• This VHDL file generates unwanted latches because not all states are defined.

```

signal sel:std_logic_vector(0 to 1);

```

- This VHDL file generates a multiplexer correctly because states "10" and "01" are defined.

- -- sel can choose either of "00","01","10", "11"

```

PROCESS (sel,a,b)

BEGIN

CASE sel IS

WHEN ``00"=>q<=a;

WHEN ``11"=>q<=b;

WHEN OTHERS=>q<=`0';

END CASE;

END PROCESS;</pre>

```

**PROCESS** (sel,a,b)

CASE sel IS

END CASE;

END PROCESS;

**WHEN** "00"=>q<=a;

**WHEN** "11"=>q<=b;

BEGIN

## **CPLD Optimization - Use of Parentheses**

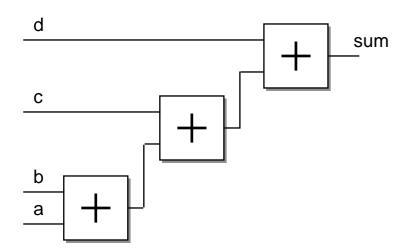

• Example listing below generates a design that uses three cascaded adders and <u>three logic levels</u>.

```

PROCESS (a,b,c,d)

```

BEGIN

sum<=a+b+c+d;</pre>

END PROCESS;

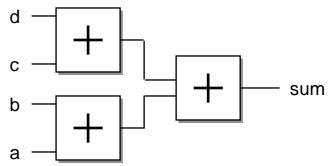

• Example listing below, by inclusion of two sets of parentheses, generates two parallel adders whose outputs the circuit then adds. This design results in <u>two logic levels</u>.

**PROCESS** (a,b,c,d)

#### BEGIN

sum <= (a+b) + (c+d);

END PROCESS;

Semiconductor Corporation

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 42

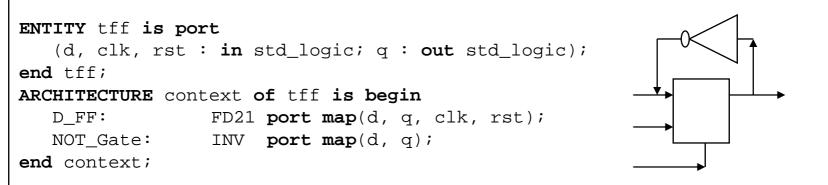

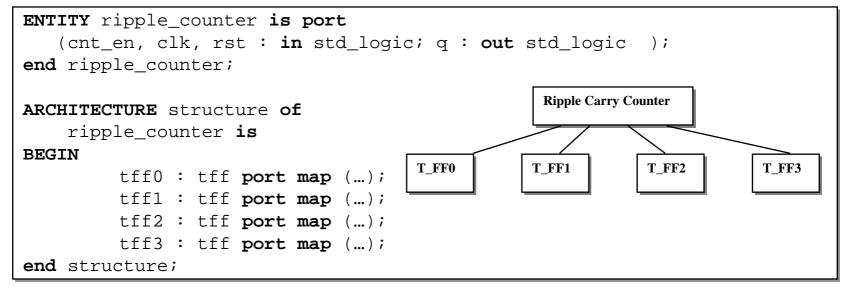

## **VHDL Hierarchical Design**

© LATTICE SEMICONDUCTOR CORPORATION 1998

FAE Training VHDL Training February 2000 43

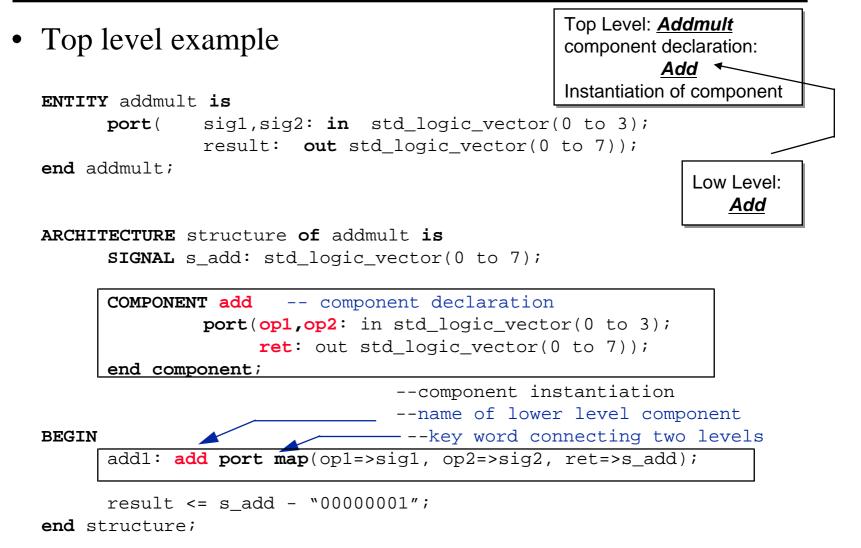

## **Concept of Hierarchical Design**

#### Low-level Design

#### High-Level Design

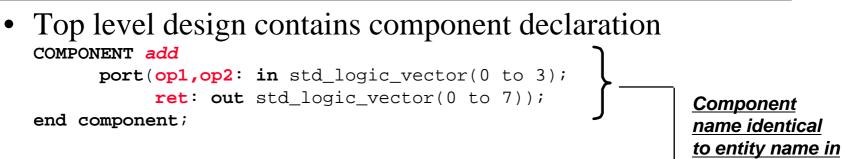

## COMPONENT

© LATTICE SEMICONDUCTOR CORPORATION 1998

LATTICE PROPRIETARY

Lattice

## **COMPONENT** (cont.)

• Lower level design of previous example

```

ENTITY add is

PORT(op1,op2: in std_logic_vector(0 to 3);

ret: out std_logic_vector(0 to 7));

end add;

ARCHITECTURE dataflow of add is

BEGIN

ret <= op1 + op2;

end dataflow;

</pre>

```

low-level design. port declaration in component and low-level entity are identical.

• Lower level design can be in a separate file or in the same file as the top-level design